File:IVE logical components diagram.jpg

Original file (951 × 737 pixels, file size: 111 KB, MIME type: image/jpeg)

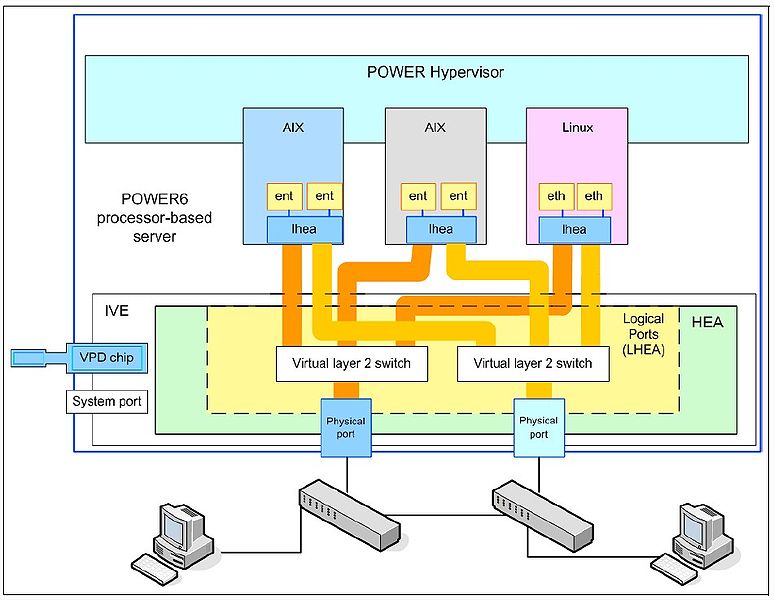

The major IVE concepts are defined as follows: HEA Host Ethernet Adapter, the key imbedded function located on the P5IOC2 I/O controller chip. LHEA Logical Host Ethernet adapter, a logical representation of a physical HEA adapter. This is the parent device of an LHEA port. LHEA port Logical representation of a physical HEA port. The maximum number of ports you can assign to an LPAR depend on the IVE feature code. Port group This is a group of logical ports that share one or two physical ports, depending from IVE feature code. Any IVE feature supports up to two port groups, and any port group supports up to 16 logical ports (LHEA port). MCS Multiple Core Scaling (MCS) is a parameter that allows multiple receive and transmit queues (QP) to be supported in each LPAR. The MCS value must be defined at port group level.

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 13:18, 6 September 2010 |  | 951 × 737 (111 KB) | Tom (talk | contribs) | The major IVE concepts are defined as follows: HEA Host Ethernet Adapter, the key imbedded function located on the P5IOC2 I/O controller chip. LHEA Logical Host Ethernet adapter, a logical representation of a physical HEA adapter. This is the parent devic |

You cannot overwrite this file.

File usage

There are no pages that use this file.